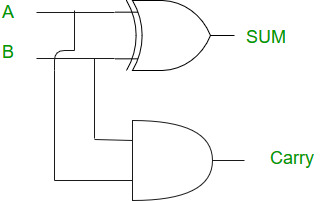

Half Adder (HA):

Half adder is the easiest of all adder circuits. Half adder is a combinational number-crunching circuit that adds two numbers and delivers a total piece (s) and convey bit (c) both as result. The expansion of 2 bits is finished utilizing a blend circuit called a Half adder. The information factors are augend and numbers to be added bits and result factors are aggregate and convey bits. A and B are the two information bits.

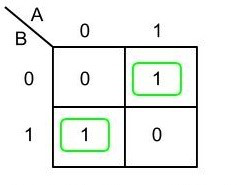

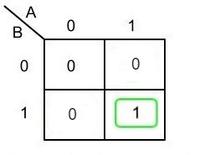

allow us to consider two info bits A and B, then aggregate bits (s) is the X-OR of A and B. it is obvious from the capability of a half viper that it requires one X-OR door and one AND entryway for its development.

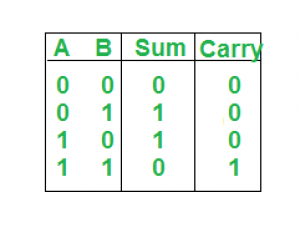

Truth Table:

Here we perform two tasks Sum and Carry, accordingly we really want two K-maps one for each to determine the articulation.

For Sum:

For Carry:

Note: Half adder has just two sources of info and there is no arrangement to add a carrycoming from the lower request bits when multi option is performed.

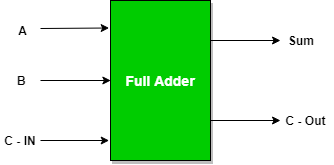

Full Adder is the snake that adds three information sources and creates two results. The initial two data sources are An and B and the third info is an info convey as C-IN. The result convey is assigned as C-OUT and the typical result is assigned as S which is SUM. A full viper rationale is planned in such a way that can take eight data sources together to make an extensive snake and outpouring the convey bit starting with one snake then onto the next. we utilize a full viper since when a convey in piece is free, another 1-cycle snake should be utilized since a 1-digit half-snake doesn't take a convey in piece. A 1-digit full viper adds three operands and creates 2-cycle results.

full

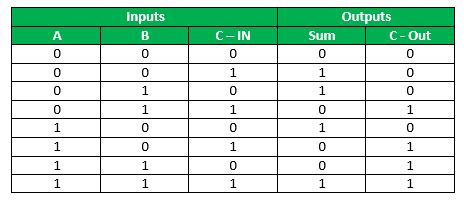

Adder Truth Table:

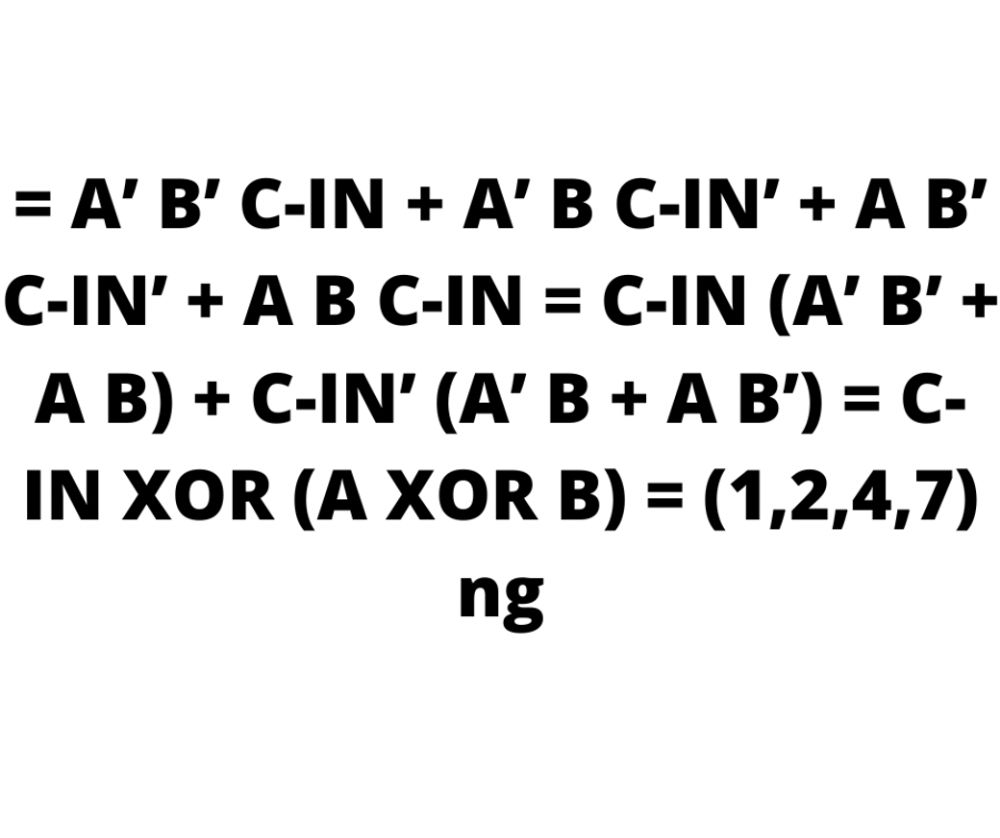

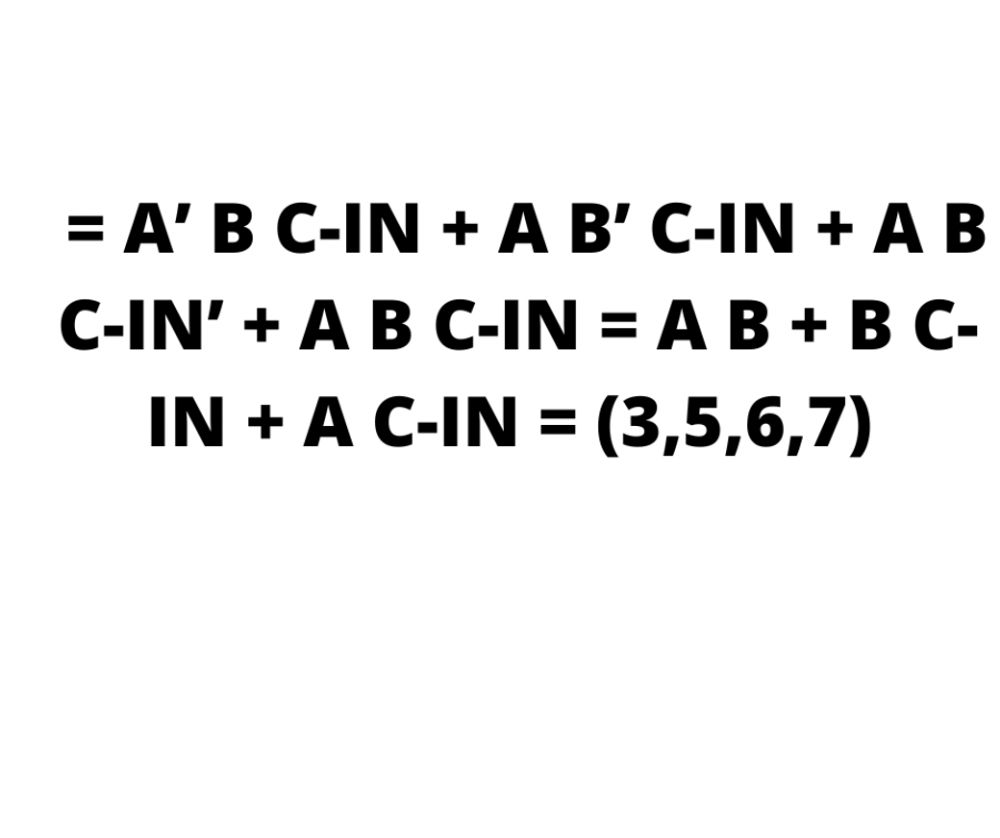

Logical Expression for SUM:

Logical Expression for C-OUT:

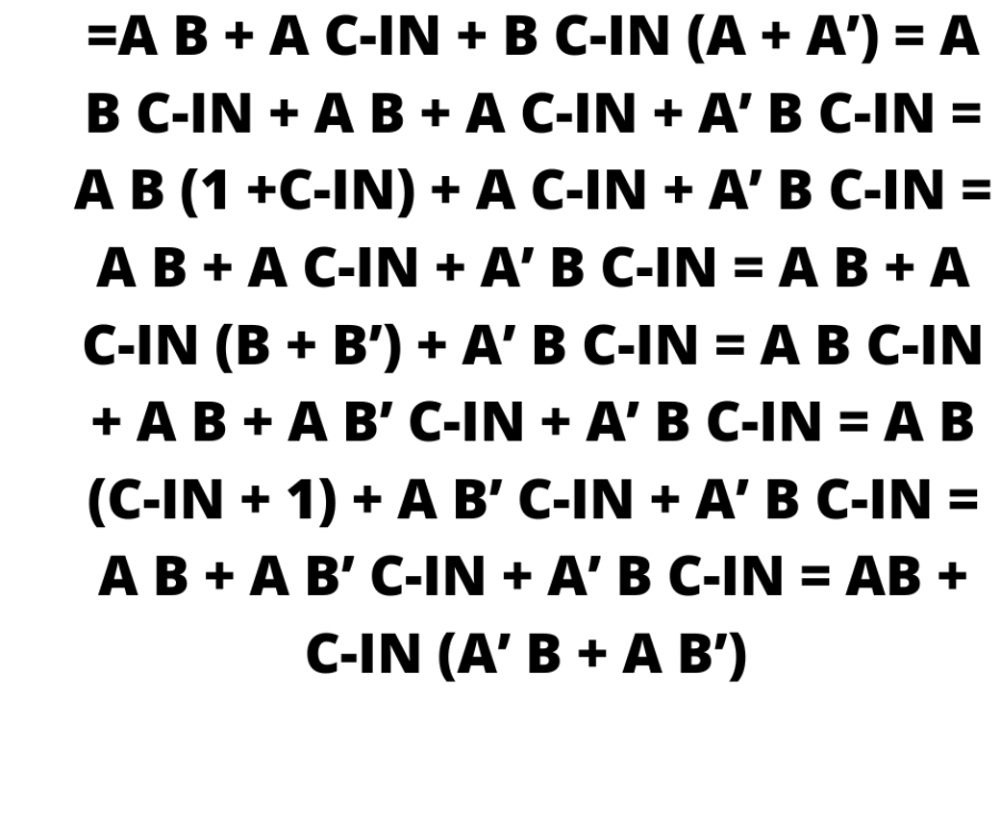

Another form in which C-OUT can be implemented:

Therefore COUT = AB + C-IN (A EX – OR B)

2 Half Adders and an OR gate is required to implement a Full Adder.

With this rationale circuit, two pieces can be added together, taking a convey from the following lower significant degree, and sending a convey to the following higher significant degree.

Total 9 NOR gates are required to implement a Full Adder.

In the rationale articulation over, one would perceive the rationale articulations of a 1-bit half-adder. A 1-bit full adder can be achieved by flowing two 1-bit half adders.